10-bit 20Ms/s SAR ADC with segmented capacitor and self-calibration comparator for industrial sensor

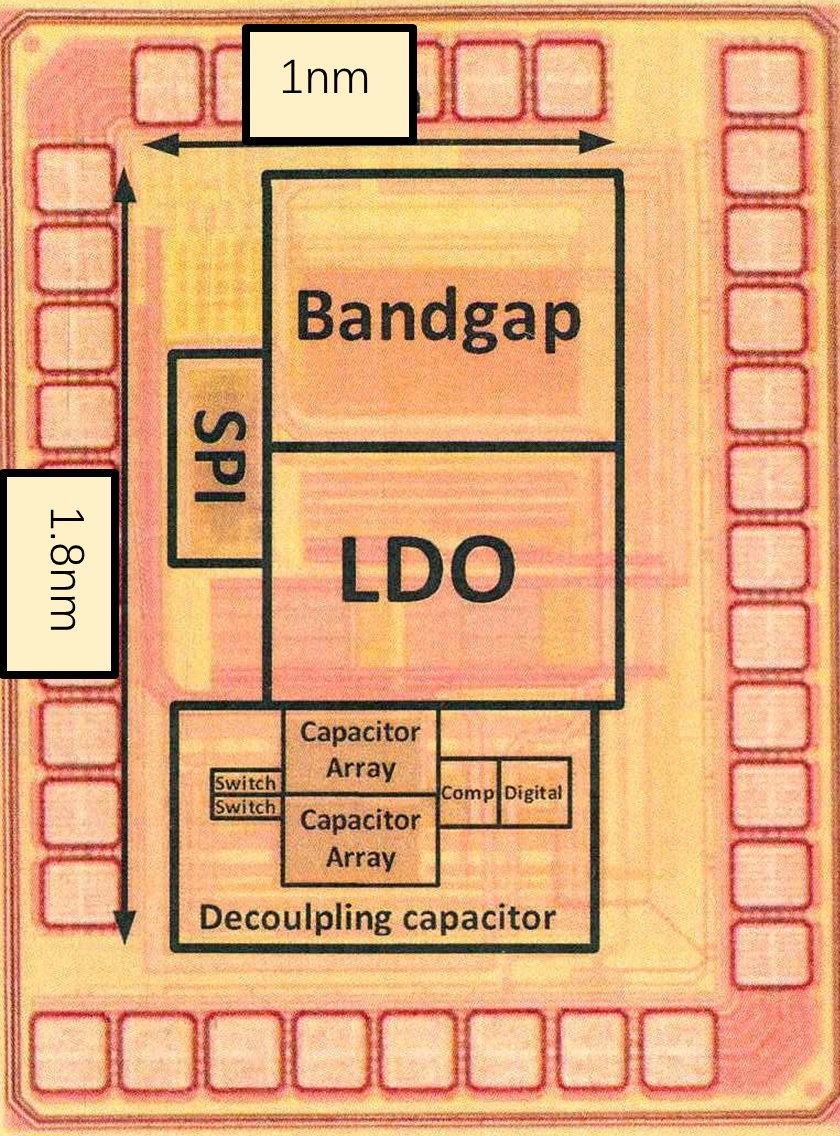

This chip is designed for the oil tank pressure monitoring system controlled by S7-1200 PLC. It collects 4-20mA analog signals from 16-channel pressure transmitters and meets the requirements of high reliability, low power consumption, anti-interference and compact integration. The chip has a built-in 1.8V reference source with temperature compensation, and a sinc3 filter in the SAR logic. It meets industrial design requirements, and can be integrated or replaced with SM1231.

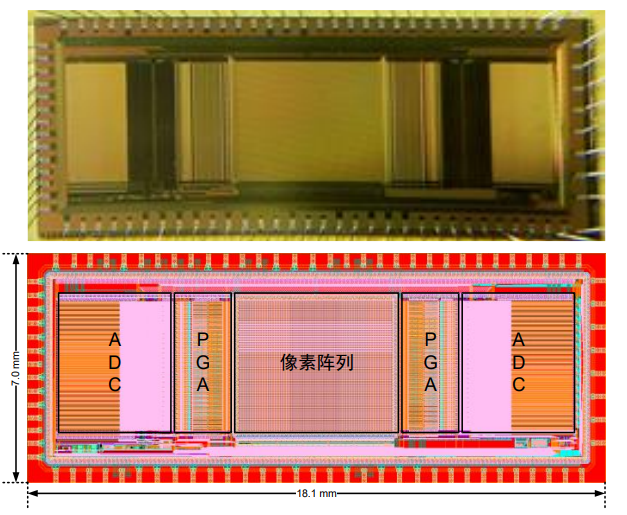

Two-step SAR ADC column readout circuit

A two-step 14-bit SAR ADC column readout circuit combining redundant capacitor array and redundant ratio-metric reference is proposed. The circuit is tape-out verified using 40 nm 1P8M CMOS process. The overall size of the chip is 0.9×0.9 mm², of which the size of the ADC core part is 218×81 μm² and the size of the single-ended capacitor array is 58×31 μm².

(only participated in Comparator and Bootstrap)

(only participated in Comparator and Bootstrap)

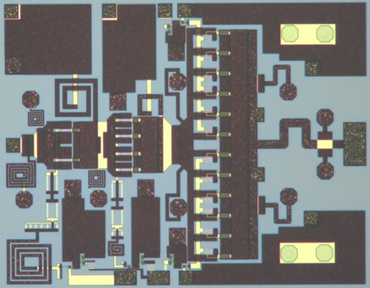

Wi-Fi 6E Power Amplifier (GaAs HBT)

This photo presents a power amplifier designed for Wi-Fi 6E using the 2μm gallium arsenide (GaAs) heterojunction bipolar transistor (HBT) process. By employing third-order inter-modulation signal cancellation, harmonic suppression, and an adaptive biasing scheme, the linearity performance of the circuit is improved. To achieve broadband performance, the power amplifier also incorporates gain distribution and multi-stage LC matching techniques. The measurement results indicate that, under a 5V supply voltage, it can achieve S21 greater than 31dB, ΔG of ±0.723dB, and P1dB of 30.6dB within the 5.125GHz-7.125GHz frequency band. The maximum linear output power, which satisfies AM-AM < 0.2dB and AM-PM < 1°, is 26.5dBm, and the layout area is 2.34mm².

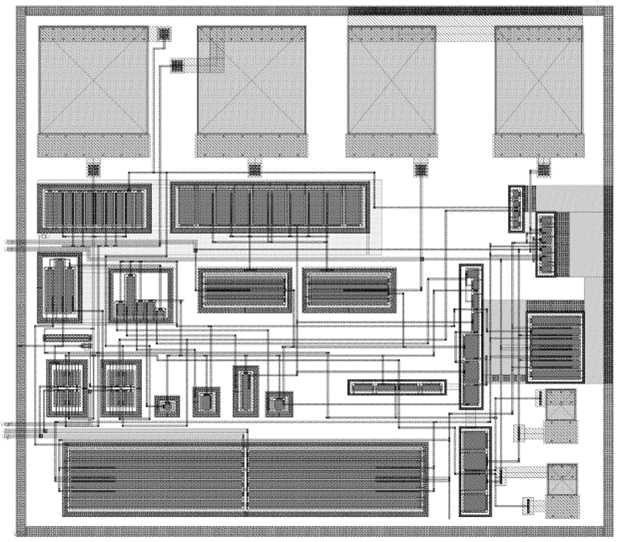

High Gain Low-Power Fully Differential Amplifier with Common-Mode Feedback

The proposed design integrates an input stage, output stage, feedforward stage, CMFB circuit, and a wide-swing biasing network, all contributing to optimized performance metrics. Simulated in a 180-nm CMOS process with a 1.8 V supply, the design achieves a gain-bandwidth product (GBW) of 111 MHz, a differential DC gain of 83 dB, and a phase margin exceeding 60° across process corners. Monte Carlo analysis confirms robust performance and low noise, validating its efficacy for high-speed, high-precision ADCs.